- #HOW TO DISPLAY SIM PANE IN MODELSIM ALTERA GENERATOR#

- #HOW TO DISPLAY SIM PANE IN MODELSIM ALTERA MANUAL#

- #HOW TO DISPLAY SIM PANE IN MODELSIM ALTERA CODE#

Make sure you understand how the code works. Think about the statements here being executed all at the same time (not consecutively, the order of declaration doesn't matter) at each rising_edge of clk. Include the signal clk to the sensitive list, and implement the LFSR logic.

Think about them as being directly connected with a wire to those registers.

The outputs prn(0), prn(1), prn(2) are assigned the respective bit values from signal D123456. Declare the asynchronous statements outside a synchronous process. The signal of 6-bit length D123456 will contain the values of the LFSR, and is initiated with seed "'000001'". Declare all the intermediate signals before the keyword begin. First, list some required IEEE library components. The code for both Verilog and VHDL is provided in the Downloads section at the bottom of the page. Now it's time to implement the LFSR module in Verilog/VHDL. DE0-Nano-SoC: Cyclone V SE 5CSEMA4U23C6N New and select Verilog HDL File or VHDL File under Design Files, then click OK. #HOW TO DISPLAY SIM PANE IN MODELSIM ALTERA MANUAL#

Use the manual for the board/FPGA you use to find the correct settings. Leave other settings as they appear by default.

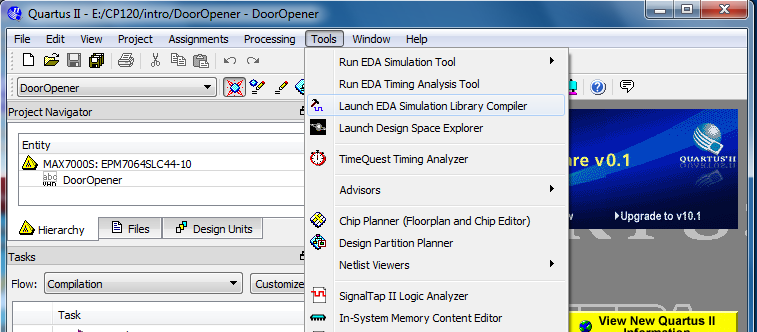

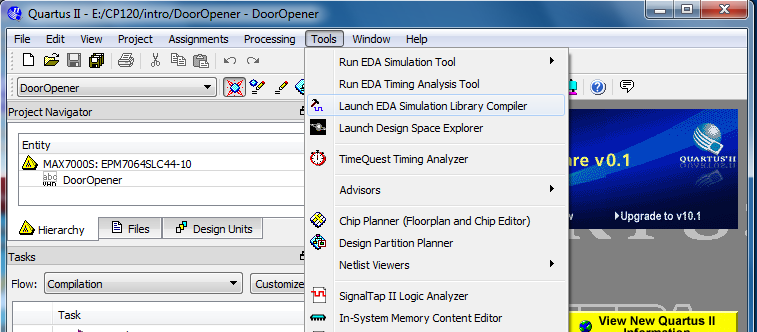

Click Next, Next, and select the Family & Device Settings depending on the board you use. Set the directory as " C:\FPGALabGroupName\LFSR_PRNG". Open Quartus Prime, go to File->New Project Wizard. Alternatively, you can create the settings manually:. For this lab you will only need a clock, keys and LEDs You can use a system builder to generate the project settings for your board. 1) Run Quartus and create a project in " C:\FPGALabGroupName\LFSR_PRNG" (so that all team members have access to it). Schematic diagram of an LFSR module with 6 registers.

For the chosen parameters, the corresponding feedback polynomial is (x^6) + (x^5) + 1 and the period is (2^6) − 1 = 63. In this lab, you will implement a 6−bit LFSR module, but only bits 2, 4 and 6 will be linked with the output.

You can think of an LFSR as a broken counter: it will go through each value a single time, however not in a consecutive order. A module with n registers will generate a pattern of (2^n)-1 different numbers, after which the pattern repeats. The initial value of the LFSR, called seed, can have any value except 0x0. An LFSR will repeatedly generate a pattern of numbers that seem random and are not biased (occur equally often). #HOW TO DISPLAY SIM PANE IN MODELSIM ALTERA GENERATOR#

A broadly used pseudorandom number generator method is based on a Linear Feedback Shift Register (LFSR) module, which is very simple, requires little resources, and is efficient. Random numbers can be approximated by pseudorandom numbers, which are not ideally random because they can be predicted and can have a bias. Generating Random Numbers using a Linear Feedback Shift Register (LFSR) Familiarize with Quartus II, ModelSim and the FPGA development board.Learn how an LFSR generates pseudorandom numbers.Learn to implement a hardware module and a testbench.Familiarize with Hardware Description Languages (HDL) such as Verilog and VHDL.

Learn the very basics about Field-programmable gate arrays (FPGAs).It's important to understand the big picture as well as the minutia, or as an engineer would say, the system and the microarchitecture. Please skim through this entire page before attempting the lab. Implementing a pseudorandom number generator using a linear-feedback shift register (LFSR) 1.3 Generating Random Numbers using a Linear Feedback Shift Register (LFSR).1 Implementing a pseudorandom number generator using a linear-feedback shift register (LFSR).

0 kommentar(er)

0 kommentar(er)